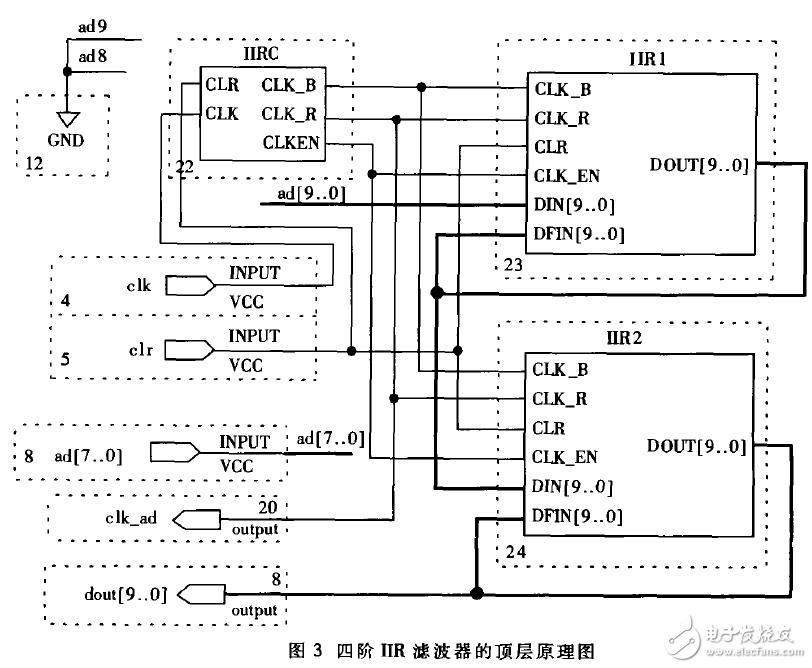

The fourth-order IIR digital filter is implemented by FPGA, and the digital elliptical low-pass filter is formed by cascading two second-order sections. The ripple in the passband is less than 0.1 dB and the stopband attenuation is greater than 32 dB. Commonly used digital filters are FIR digital filters and IIR digital filters. The FIR digital filter has precise linear phase characteristics, is widely used in signal processing, and can be designed using the FIR core filter IP Core designed and debugged in advance. In addition, for the same design index, the FIR filter requires 5 to 10 times higher order than the IIR filter, the cost is higher, and the signal delay is larger. The order required by the IIR filter is not only lower than that of the FIR filter, but also the design result of the analog filter can be utilized, and the design workload is relatively small. The IIR filter implemented by the FPGA also has various advantages.

The digital filter is actually a linear time-invariant discrete system implemented by a finite precision algorithm. Its design steps are as follows: firstly, its performance index is determined according to actual needs, and then the system function is obtained, and finally the finite precision algorithm is used. According to the needs, the design index of the system is: the sampling frequency of the analog signal is 2MHz, and the minimum sampling time is 20 points per cycle, that is, the passband edge frequency of the analog signal is fp=100kHz, the stopband edge frequency is 1MHz, and the passband fluctuation is not more than 0. .1dB (passband error is not more than 5%), and the stopband attenuation A s is not less than 32dB. The calculation of the system function is more convenient with Matlab software.

This paper uses a compromise method, that is, the multiply-add unit (MAC) multiplier uses an array multiplier instead of a serial multiplier to increase the speed of the operation. It should be noted that the multiplication operation in the LPM library of MAX+plus II is an array multiplication of unsigned numbers, so it is necessary to convert two complementary code multipliers into unsigned numbers and then multiply the products into complements. Code product output. It takes a total of 6 clock cycles to complete each operation of each second-order section, and a separate two-stage pipeline structure is required by using separate MACs, that is, each data passes through two second-order section outputs and only takes 6 clock cycles.

Copper Lugs,Copper Cable Lugs,Plating Copper Cable Lugs,Copper Tube Terminal Lugs

Taixing Longyi Terminals Co.,Ltd. , https://www.lycopperterminals.com